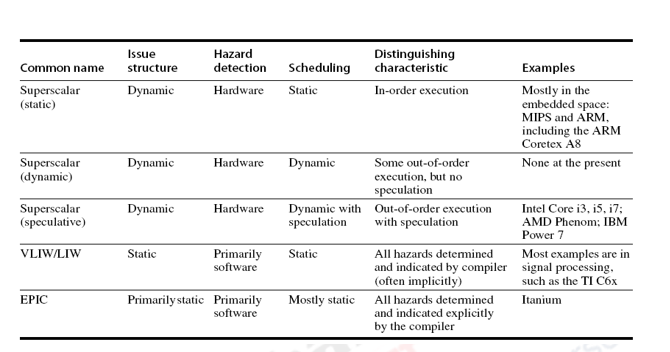

![Implementing DIE in a Superscalar Processor, as proposed in [24]. The... | Download Scientific Diagram Implementing DIE in a Superscalar Processor, as proposed in [24]. The... | Download Scientific Diagram](https://www.researchgate.net/profile/Sudhanva-Gurumurthi/publication/4079956/figure/fig1/AS:670000645939224@1536752010888/Implementing-DIE-in-a-Superscalar-Processor-as-proposed-in-24-The-gray-shaded-area-is.png)

Implementing DIE in a Superscalar Processor, as proposed in [24]. The... | Download Scientific Diagram

Modern Processor Design: Fundamentals of Superscalar Processors eBook : Shen, John Paul, Lipasti, Mikko H.: Kindle Store - Amazon.com

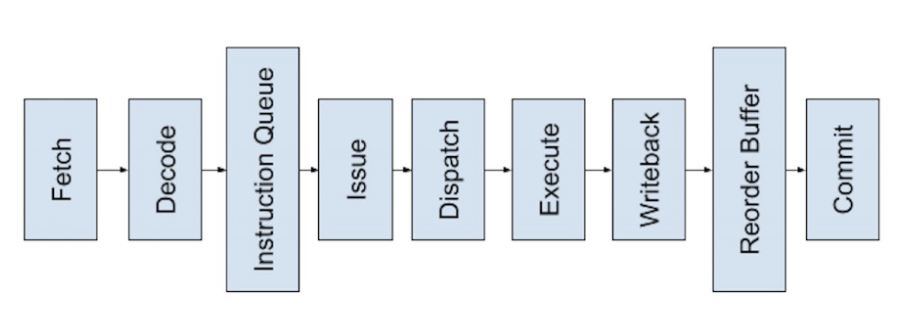

Superscalar Processors: Branch Prediction Dynamic Scheduling Superscalar Processors Superscalar: A Sequential Architecture Super

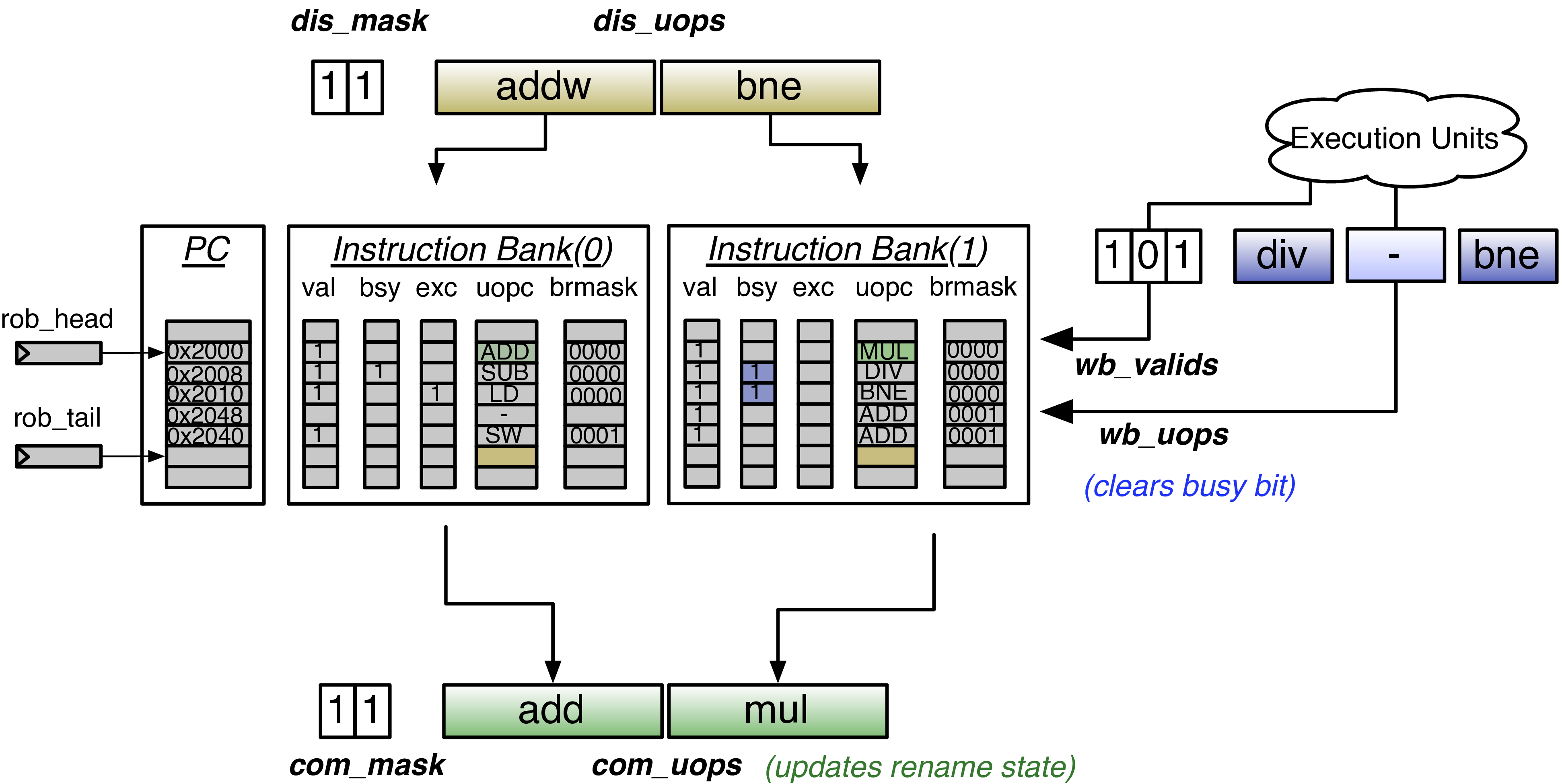

![PDF] Out-of-Order Retirement of Instructions in Superscalar, Multithreaded, and Multicore Processors | Semantic Scholar PDF] Out-of-Order Retirement of Instructions in Superscalar, Multithreaded, and Multicore Processors | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/74afef9d15562591c406de0b6bd97cc70d67b07f/20-Figure1.3-1.png)

PDF] Out-of-Order Retirement of Instructions in Superscalar, Multithreaded, and Multicore Processors | Semantic Scholar

GitHub - dsesami/superscalar-processor-model: A nine-stage out-of-order superscalar processor pipeline.

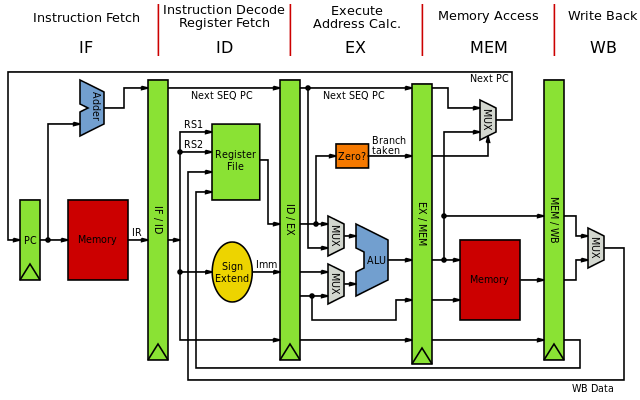

![PDF] The microarchitecture of superscalar processors | Semantic Scholar PDF] The microarchitecture of superscalar processors | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/02f274f3569685b0f37abf6760e5386b8813353e/8-Figure4-1.png)

![PDF] Complexity-effective reorder buffer designs for superscalar processors | Semantic Scholar PDF] Complexity-effective reorder buffer designs for superscalar processors | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/db225f78a0a32418722f42dead2de59cba343331/3-Figure2-1.png)